Synphony HLS Solution

Synopsys launched its newly developed Synphony HLS (High Level Synthesis) solution. The solution integrates the M language and model-based synthesis method. Compared with the traditional RTL process, the solution can provide communication and multimedia applications with up to 10 times the speed of higher design and verification capabilities. Synphony HLS generates optimized RTL for ASIC and FPGA applications, architecture and rapid prototyping.

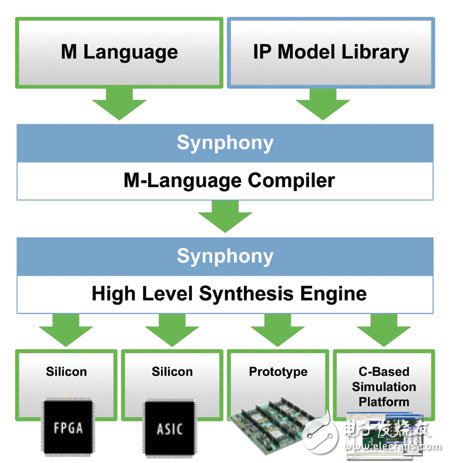

Synphony HLS solution architecture diagram

Chris Eddington, Synopsys' high-level integrated approach and system-level marketing director, said that the Synphony HLS solution can significantly change the way ASICs and FPGAs are used in system verification and embedded software development. The traditional HLS method continues to undertake important hardware engineering resources, translating algorithms into RTL, and running them on ASIC and FPGA chips. Synphony HLS can use MATLAB for high-level simulation and product coding, which means that it took months or years to reach the hardware from simulation. Now it can be completed in just a few hours or days using the Synphony HLS solution.

Chris Eddington said that the main reason for this is that the MATLAB environment of Mathworks can express concise behavior at a very high level of abstraction, and it has been widely used for algorithm exploration and design. The M language model developed in this environment is usually re-encoded and re-verified under the RT level (RTL), and in some cases implemented and verified in C/C++. Unlike the inefficient and error-prone manual recoding process, Synphony HLS creates executable RTL and C models directly from high-level M language coding and Synphony HLS—an optimized IP model library. By adopting the unique constraint-driven fixed-point propagation function, designers can quickly and intuitively obtain fixed-point models from a synthesizable subset of high-level floating-point M codes. Then Synphony HLS engine will synthesize the RTL optimized from the architecture to meet the target requirements of area, speed and power consumption. Synphony HLS allows designers to retain their favorite algorithm modeling language without recoding and revalidating the model, thus ensuring early system-level verification and verification.

It is understood that the Synphony HLS engine can comprehensively optimize the architecture for ASIC, FPGA, rapid prototyping or virtual platforms, while maintaining the consistency of verification through various levels of implementation processes. Taking into account the user-specified goals and architectural constraints, the HLS engine can automatically optimize at multiple levels by applying wiring, programming and constraint optimization on the language and model boundaries (including M language and IP modules) and the entire design level.

For ASIC design, Synphony HLS has a new advanced timing evaluation function. With a given ASIC technology, it can automatically use Design Compiler to obtain the precise information required for automatic wiring and fast timing closure. For FPGA design, Synphony HLS can also provide advanced timing and specific device optimizations for a wide range of FPGA product series (such as Actel, Altera, LatTIce, and Xilinx FPGA vendors). This includes optimized mapping of hardware multipliers, memories, shift registers, and other advanced hardware resources in today's FPGA devices.

Chris Eddington said, "With Synphony HLS, we are able to provide a faster and more reliable method for system and software verification than our competitors. Combining Synopsys' leading system prototype and hardware-assisted verification solutions, design teams can be more Design and verify their complex chips and software more economically and more reliably."

Pv Combiner Box,Photovoltaic Combiner Box,Solar Power Combiner Box,Pv Array Combiner Box

Zhejiang Kaimin Electric Co., Ltd. , https://www.ckmineinverter.com