Static Leakage Current Issues in IC Design

After the chip is shuffled, the static leakage current of the chip needs to be tested to meet the standard. If the quiescent current of the chip is too large, the battery-powered chips, such as mobile phones and notebook computers, will seriously affect the standby time and make the chip Market competition is at a disadvantage, so static power consumption needs careful consideration.

I was responsible for a back-end design of a SOC chip five years ago. The chip embedded SRAM, eeprom and other modules, the chip's front and back end design and verification are very full, and there are no problems in the FPGA board verification, can be described as everything has only Owing to the east, we waited for the chip to come back and test it. The chip did not bear the "core man." The chip came back. All of the functional tests in the test engineers' different test vectors were very smooth. Different Worst, Type, and Best Corner can all pass normally, which can be described as a double harvest of timing functions.

In the test chip AC parameters such as PAD high and low, but also to meet the design criteria. The quiescent leakage current of the tested chip also reached the target of 10uA. Everyone thought that the design was very successful. However, problems have been found in the reliability test and yield analysis of the chips. Some chips have a maximum leakage current of 300uA and a minimum leakage current of 2uA, and they are linearly distributed from the probability of the test chip.

It was found that all kinds of different power-up sequences were used, such as 1.8v and 3.3v, all inputs were connected to a fixed level such as VDD or VSS, but all bidirectional PADs were in the output state to prevent the input from floating. As a result, the leakage current becomes larger. However, the chip leakage current is still large, and the leakage is small or small. So I think it is caused by foundry manufacturers production yield problems? I also consulted a foundry on this issue. The manufacturer also gave me many suggestions. For example, after checking the PCM parameters after production, if the manufacturer has 10 sampling points on the wafer, if there are one or two PCM parameters A small amount of distortion belongs to the more normal design range. Found the PCM parameter table returned by the foundry home after production, download the PCM parameters on the production site before production, careful comparison of only one test point has a NMOS domain value voltage is a bit excessive. Afterwards inquiring about the design chip of MPW that we do together, their chip is very normal in quiescent current, with the design index uA grade, the fluctuation does not exceed 2uA. This eliminates the problems that may be caused by the yield of foundry production.

In the long test and discussion, front-end and back-end design engineers think that their design is no problem, and even in the bottom of the heart are skeptical of the other design flaws, but did not rise to the open table quarrel. Later, in desperation, I thought of a method that was to do EMMI (ie, a low-light photo shoot). The low-light photo was taken in Shanghai Yishuo. Photos were sent back. Sure enough, there were bright spots in the few chips with the largest leakage current. The highlights are in the same position, and there are bright points in the supplementary notes that there is a large leakage current. The location of the chip where the highlight is located is in the digital logic, not in the analog position of the chip. If it is an analog part, it is better to say that if there is a large current comparator or amplifier, there will be PMOS and NMOS at the same time. Current. If the short-circuit current is greater than 80uA, it will also be shot at EMMI. Since it is on digital circuit gates, only two types can cause large currents:

Case 1: The MOS layout design in this area does not satisfy the design rule of foundry given latch up, which results in a sharp increase in the positive feedback current of the MOS due to the parasitic triode. Positive feedback is uncontrolled until the MOS is damaged.

Case 2: It is possible that the input terminal of the digital gate circuit is floating, which may cause the PMOS and the NMOS to be turned on at the same time, and there is a short-circuit current. If the size of the MOS transistor is larger, the leakage current will be larger.

From the instinctive, I first doubt that the backend layout is not a problem, according to the photo on the bright, through the top of the photo visible and the underlying layer of the relatively large stripe metal power ground, the positioning of the logic gate device is A relatively big BUF unit, I saw enough well taps and sub taps in the layout, and all the BUF's MOS units are not more than 20 microns away from the tap. I can be sure that it will not happen on the layout. Up effect. Assume that if the entire latch up occurs, because the latch up is controlled, the functional logic of the unit must fail to appear on the functional test, and it is permanent and cannot be recovered until the area's The MOS device is burned unless the power is turned off in time, and it will happen as soon as power is turned on. But the logical function analysis of the logic function of the BUF unit does not make mistakes, and the test is also normal at high temperatures, the higher the temperature from the point of view of the latch up the more likely to occur latch up. So further formal is not latch up The resulting large current.

Another possibility is that the input to the BUF is floating, causing a large short-circuit current from VDD through the PMOS NMOS to GND. From the bright spot of the BUF's first inverter, I used SPICE simulation to add a 1K ohm resistor to the GND and NMOS transistors. The input analog voltage plus an indeterminate logic state The maximum leakage current test is around 80uA, which is in line with the EMMI highlights the required current conditions. Then the input of chasing BUF comes from, and finally finds out the output of connecting eeprom, then is the output of eeprom is not high resistance of Z, looking for circuit personnel to analyze the document of eeprom does have the state of output Z , And controlled by the OEN signal, but the output is high resistance when OEN is high, it happens that the test leak current condition OEN is always not high, because the voltage in the high impedance buffer is randomly distributed, in the test leakage current statistical distribution There is a random magnitude of current between maximum and minimum. Good guys found the problem, and later the front-end engineers modified the test vector. When the leakage current was measured, the EEPROM was low and the output of the eeprom was a stable logic state. Sure enough, there was a 300uA chip leakage current that returned to the 2uA leakage current. This seemingly simple problem, if you do not pay attention in the design, will bring a lot of trouble, in fact, the back-end engineers are also responsible, if you carefully look at the file, you can have a high resistance in the output like SRAM EEPROM The pin first-level cell selects the mos gate device as small as possible, and even if a high resistance causes a short-circuit current, it is also very small.

To sum up, engineers need good communication before and after the chip design to make up for the lack of knowledge at all levels and to raise as many possible risk issues as possible. Only in this way can a good chip be made.

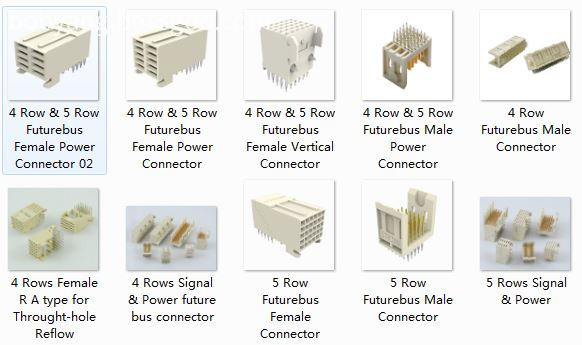

Future Bus connectors Description

Future Bus connectors, which use 2mm style have a mating distance of 10mm. Both Future bus and the upgrade Future bus+ are out-dated.No additional work has been done to upgrade the specification over the years. However we still produce products which meet the Physical and Electrical layers of IEE P896.

Antenk future bus connecto feature

designed in metric dirnension on 2 millimeters grid over 5 rows.

1 Standardized product through EIA (USA), IEC and CECC (international).

2 Selected by IEEE as the interconnection system for Futurebus + / SCI / VicBus.

3 Multi-sources product,use for telecommunication, network, server / workstation market.

4 High tempersture materials SMT compatible.

5 Modular design giving flexibility for system design.

6 Stackable end to end without loss of contact position.

7 High density (more than 2 times as compared to the standard inch based " Euroconnector DIN 41612" ).

8 Tuning Fork female contact concept for higher robustness and improved reliability

(low contact resistance and high normal force).

9 Low insertion force design.

10 Inverse connector system (signal and power).

11 Optimized solder and compliant press-fit terminations for backplane and circuit board connectors.

12 differents mating lengths on signal and 3 on power for standard connector system.

Future Bus connectors Application

Telecom backplane board

Antenk offers a complete line of 5+2 and 8+2 Hard Metric Connectors as well as a complete line of 4 and 5 row Future bus Connectors.

4 and 5 row Future bus Connectors

4 Rows Signal & Power

5 Rows Signal & Power

Female IDC Type 4&5 Rows

Power Connector & Cable

Shroud

Vertical, 5 Rows

Right Aangle, 5 Rows

Vertical, 4 Rows

Right Angle, 4 Rows

5+2 and 8+2 Hard Metric Connectors

2.0mm Future Bus Connector Male DIP

2.0mm Future Bus Connector Female DIP

2.0mm Future Bus Connector Male Press Fit

2.0mm Future Bus Connector Female Press Fit

2.0mm Future Bus Connector Power Type

2mm HM (hardmetric) Connector Introduction

System designed to meet the current and future needs of instrumentation applications giving excellent electrical and mechanical characteristics. It is a high performance, high density system with flexible configuration which offers upgradeability. The connector system is fully supported by Antenk spice models to guarantee choosing the right product to match the application.

ANTENK 2.0mm HARD METRIC CONNECTOR MODULES comply with international IEC 917and IEC 61076-4-101

standards. The connector systems in telecommunication and other industries require hight density connectors to support

larger amounts of data increasingly higher speeds antenk 2mm hardmetric modules offer the solution

Features and Benefits:

This high density connector modules can be stacked end to end without loss of space.

1,ANTENK developed the 2.0mm series under thorough consideration of impedance match, propagation delay,

cross talk, reflection. It is the ideal connector for digital high speed data application.

2,ANTENK offers differend types with inverted mating configuration. The male connector is a fixed module at the

backplane and the female commector is a free component of the plug-in module. The male connector has 5 signal row.

3 The outer shielding rows z and f of the male connector engage the shielding contacts of the famale connector. theshield

is also designed for gas tight, press-fit installation.

4 The connector system offers 15 contact length that utilize the proven press-fit assembly technique. Within the 15

contact length are 3 mating levels, achievable on both the plug-in and rear I / 0 side.

5 Coding system prevents mix-up and wrong mating between male and female connectors.

6 The 2.0mm hard metric connectors and DIN 41612 connectors can be used on the same PC board as both have the

same mating distance.

7 Staggered make-break pin populations for optional hot-swap capability.

8 Rear pin option for through-the-backplane I/O application.

9 High density PCI capability,shield for EMI/RFI protection.

2mm HM (hardmetric) Connector Features:

High density system with small real estate on backplane and daughtercard

Extensive range of signal, power, coaxial and fibre board-to-board and cable-to-board connections

Modular units give flexible configuration

Special versions for VME64 extensions and CompactPCI

Signal contact rating 1.5a fully energized

Universal power module rated at 7.8A/line, 23.4A fully energized

All lines impedance controlled to 50 (single ended) and 100Ω (differential) nominal

Safe design, complies with IEC950 in mated condition

Universal power module is safe in unmated condition

Several performance levels for board and cable connectors with unshielded and shielded versions

Mismatching keys block mating before any contact touch

Small press fit board hole allows maximum track width and minimum signal corruption

1.4 to 5.6mm (0.055 to 0.220 inch) Backplane thickness range

2mm HM (hardmetric) Connector Applications

Communications & Networking, Computers & Computer Peripherals, Sensing & Instrumentation

Metric Connectors,2.0Mm Hard Metric Connectors,Hard Metric Connectors,Hard Metric Female Connector,2.0mm Future Bus Connector Male DIP,2.0mm Future Bus Connector Female DIP

ShenZhen Antenk Electronics Co,Ltd , https://www.atkconnectors.com