The importance of micro-encapsulation technology to mitigate satellite loads

With the requirements of aerospace systems for miniaturization, low power consumption, high performance, and high reliability, the shortcomings of conventional PCB system design solutions are becoming more and more obvious. Due to the limitations of chip and module size and power consumption, PCB board size and power consumption cannot be reduced indefinitely. The package size of a single chip is usually on the order of mm to cm, but the trace length on the PCB is usually on the order of 1cm~50cm. Excessive package and traces cause large loss and many parasitic parameters, which limits the system performance. . At the same time, due to the complicated function of the system, the use of a large number of discrete devices causes many system failure points, and the reliability of the whole machine is reduced.

In order to solve the drawbacks of traditional on-board system design, the aerospace industry has gradually begun to adopt micro-package and micro-assembly technologies widely used in communications, computers and consumer electronics to improve system integration and reliability.

Typical micro-package and micro-assembly technologies include SoC, MCM, SiP, SoP, and the like.

SoC technology first appeared in the 1980s, it is used to integrate multiple functional modules into one chip, mainly used in high-performance fields such as communication, computer, network, etc. Typical such as NVIDIA Tegra, Freescale Vybrid and the following figure Show Intel's Core series multi-core processors. The SOC is characterized by the integration of multiple functional modules of the same process onto a single chip. The system performance is high and the power consumption is low. It is the first choice for commercial integrated chip solutions. The basic requirement is to achieve on the same semiconductor material. For the aerospace industry, which combines GaAs, GaN and silicon germanium processes, it is more difficult to achieve.

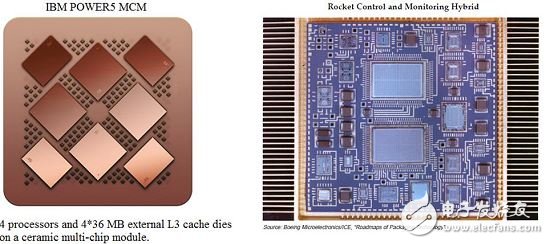

MCM is also a kind of packaging technology that emerged in the 1980s. It is characterized by integrating multiple chips and even bare Dies into a package through gold wire bonding wires and substrate materials. The module size and cost of the MCM package can be reduced a lot, and since the individual chips in the module do not need to be separately packaged and the traces between the chips are shorter, it can provide better transmission performance. In addition, due to the high degree of integration, it is easy to perform centralized shielding and protection, so the reliability is higher than that of the discrete device system. MCM technology can integrate different process chips into one package, so it is very flexible and can be used to build analog, digital, RF and hybrid systems of resistors, capacitors and other passive components. The following figures are two MCM chips developed by IBM and Boeing.

Figure 1: IBM Power5 processor and Boeing's MCM control chip

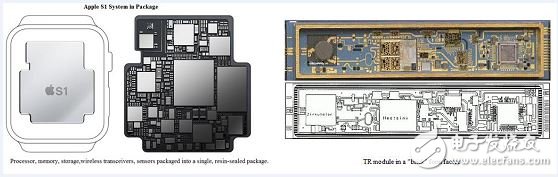

SiP is a packaging technology that emerged in the 1990s and can be considered an upgraded version of MCM technology. In addition to the planar packaging of many different process wafers like the MCM, the SiP packaging technology can also perform stereoscopic 3D stacking of bare Die or package, further increasing the packaging density. It is widely used in portable consumer electronic devices such as mobile phones and PADs, such as the core modules of Apple in iWatch and the T/R modules used in phased array radars.

Figure 2: SiP module and RF T/R SiP module used in iWatch

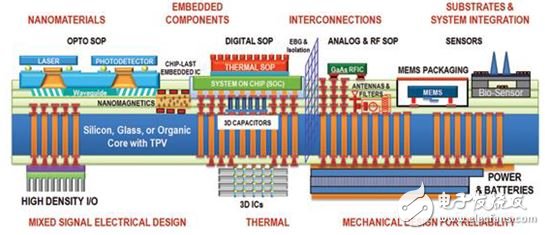

SoP is a packaging technology that emerged at the beginning of this century and can be considered as a further upgrade of SiP technology. In addition to SiP, which can complete 3D stacking and packaging of various wafers and passive components, thin film technology and nano materials are used to put some commonly used passive components such as resistors, capacitors, filters, waveguides, couplers, antennas and even Biosensors and the like are directly integrated on the package substrate. This reduces the trace length on the substrate from the order of mm to the order of um or even nm, further improving system performance and integration. The figure below is an example of a SoP chip application.

Figure 3: Typical SoP System

It can be seen that SoC, MCM, SiP, SoP and other technologies have their own characteristics and application fields. In order to realize the miniaturization and reliability of aerospace electronic systems, MCM and SIP are especially suitable for micro-package and micro-assembly technology that can be adopted in system-level miniaturization design. At the same time, we can focus on the development of SOP technology and make corresponding technical reserves.

Micro-packaging and micro-assembly technology can bring significant integration and system performance improvements, but it is difficult to design and test due to the completely different technologies and processes used in traditional board-level system design. Especially for applications such as space and high radiation, high reliability applications, how to carry out reliability design and comprehensive and effective functions and performance verification is especially important. The main difficulties and challenges of using micro-encapsulation technology in space applications are reflected in the following aspects.

1. Design and simulation of micro-encapsulation materials and interconnection technologies: In space applications, the working environment of radiation, temperature, vibration, etc. is harsh. The working cycle of a satellite may take more than 20 years and is almost non-repairable, making it reliable. The requirements are high, so the choice of packaging materials and interconnect technology is critical. In terms of the base material, there may be various choices of plastics, resins, aluminum, ceramics, etc. For dielectric materials, BCB (benzocyclobutene) materials, Riston and Kapton materials, etc. are suitable for harsh environments such as space; In terms of technology, there may be spherical soldering, gold wire bonding, TSV, etc., and in the mainstream gold wire bonding method, there are various bonding wire structures. Therefore, it is a difficult and key technology for system design to simulate various material properties, processing techniques, and routing topologies and to determine the design scheme while ensuring that the electrical, thermal, and mechanical performance requirements of the space environment are met.

2. Function and performance verification of key chips: The micro-package module packs chips of different functions and even bare Dies together and bonds them together by gold wire. There may be several or even dozens of sub-function modules inside the module. . Because the cost of aerospace-grade chips is very high, if one of the chips is found to be defective after packaging, the entire module will be scrapped. Therefore, the function and performance of the chip before the package is tested to improve the final yield and reduce the cost. important.

3. System function and performance test of micro-packaged modules: Most micro-packaged modules package two or more functional modules such as analog, RF, digital, power supply, etc. with metal or ceramic materials. After each functional module is packaged together, the function and performance of the micro-packaged module need to be thoroughly tested to ensure that the packaged module functions and performance meet the design requirements. For high-reliability applications, environmental aging tests and screenings are also required to ensure reliable and efficient operation in the next few years or even decades, which makes the system function and performance testing of micro-packaged modules critical. important.

1. High-speed parallel and serial conversion chip function and performance test

Parallel bus is the earliest and most commonly used bus structure in digital circuits. In order to solve the problem that the parallel bus occupation size is too large and the wiring length is too demanding, with the development of chip technology and the speed increase, more and more digital interfaces start to adopt the serial bus.

In order to facilitate the transmission of multiple parallel digital signals with as few cables as possible, and to provide better noise suppression and transmission distance, multiple parallel data are generally multiplexed together by high-speed TRANSCEIVER chip and passed through high-speed low-voltage differential. The signal is transmitted.

After the data rate is increased, the requirements for impedance matching, line loss, and jitter are higher, and signal quality problems are easily generated with little attention. For the testing of high-speed serial transceiver chips, the following aspects are mainly involved:

* High-speed serial chip transmitter signal quality test: including output amplitude, eye diagram, jitter, rise time, fall time, etc.;

* High-speed serial chip receiver jitter tolerance, noise tolerance, sensitivity, system error rate test, used to verify the actual transmission error rate, receiving tolerance and so on.

* Chip operating voltage, current, power consumption, etc.

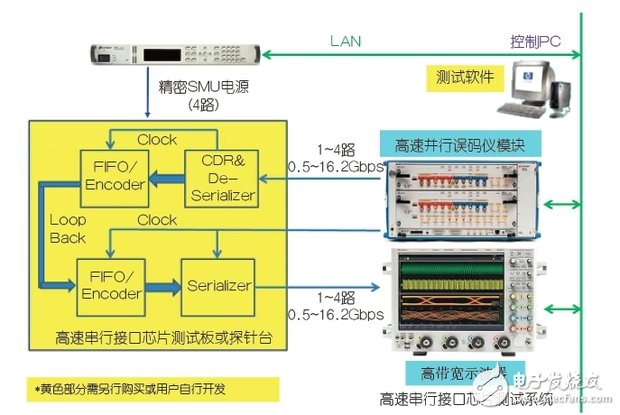

The following is the test platform composition of the entire high-speed transceiver chip transmission system.

Figure 4

In the test, a high-performance multi-channel BER tester is used to generate multiple serial excitation signals and clocks to be sent to the tested chip. After loopback, the data is sent back to the BER tester for bit error rate statistics or high-bandwidth oscilloscope for signal quality analysis. During the error rate test, random jitter, deterministic jitter, common mode noise, differential mode noise, and ISI intersymbol interference can be added to the signal to verify the receiver's tolerance for bad signals.

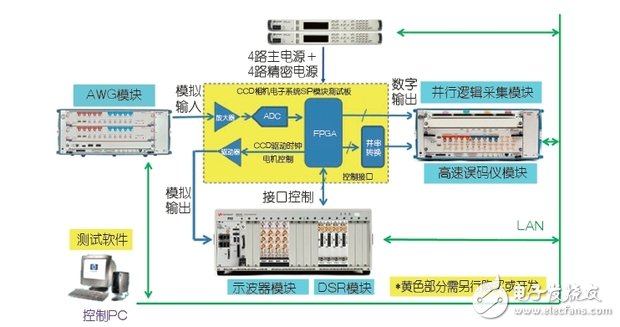

2. Satellite camera imaging electronic system micro-package module overall test plan

Its test system should include the following features.

* Simulation of CCD signal: It should be able to simulate the analog signal output by the CCD device, and can flexibly increase the noise to verify the ability of the module under test to extract and recover image data.

* Acquisition and analysis of high-speed output data: It should be able to capture and capture the high-speed data output processed by the module under test, and extract the image information in the data according to the data structure to verify the function and performance of the module under different working conditions.

* Analysis of analog output signal: Measure and analyze the amplitude, frequency, duty cycle, pulse width, etc. of the drive signal such as CCD drive clock and motor/shutter.

* Interface control circuit: should be able to control the module into normal working condition.

* Module power consumption and power immunity test: It should be able to record the voltage, current and power consumption of the module under different working conditions, and can simulate abnormal conditions such as voltage drop, power supply ripple, power-on and power-off timing changes, and verification module. Working condition in extreme cases

Figure 5: CCD camera SiP module test system

In the test, the high-performance AWG arbitrary waveform generation module is used to simulate the video analog signal generated by the CCD output, which is output and processed in high-speed digital form after being collected and processed by the module under test. In the case of parallel data capture of high-speed parallel data, high-speed logic analyzer modules can be used to capture the analysis; in the case of multiple high-speed serial data, the input of the parallel BER tester can be used for clock recovery and data capture. The test requires that the signal-to-noise ratio, dynamic range, bandwidth and other indicators of the AWG module can meet the system signal-to-noise ratio test requirements, and can flexibly add noise and other interference factors, and have enough deep memory to generate the signal of the entire video frame. The logic analyzer should have a high enough state sampling rate and memory depth. The BER tester should have multiple serial data input capabilities, clock recovery capability, high speed signal equalization capability, and sufficient memory depth.

Fabric Bluetooth Speakers,Fashion Fabric Bluetooth Speaker,Portable Bluetooth Speaker,Tws Bluetooth Speaker

Comcn Electronics Limited , https://www.comencnspeaker.com